Probabilistycznie szybciej

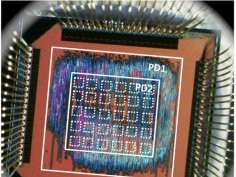

Przed trzema laty profesor Krishna Palem z Rice University zaprezentował pierwszy procesor probabilityczny (PCMOS - Probabilistic CMOS). Teraz pokazano jego doskonalszą wersję, a praca na jego temat została uznana podczas ACM Computing Frontiers za najlepszy dokument tego typu.

Profesor Palem od 2003 roku prowadzi badania nad procesorami probabilistycznymi. Uczony uważa, że warto poświęcić nieco dokładności w obliczeniach, nie korygować powstających błędów, a w zamian za to uzyskać znaczny przyrost mocy przy jednoczesnym zmniejszeniu poboru energii. I rzeczywiście. Pokazany właśnie procesor jest co najmniej 15-krotnie bardziej wydajny niż współczesne chipy.

Już w 2011 roku podczas symulowanych testów zespół Palema wykazał, że zredukowanie niektórych części tradycyjnego układu scalonego powoduje, że jest on mniejszy, zużywa mniej energii i szybciej przeprowadza obliczenia. Nasze najnowsze testy pokazują, że taka redukcja układu powoduje, iż zużywa on 3,5 raza mniej energii, przy jednoczesnym zwiększeniu liczby błędów w obliczeniach o 0,25%. Gdy weźmiemy pod uwagę zyski na prędkości obliczeń i zmniejszeniu rozmiarów, to taki układ jest 7-krotne bardziej wydajny od zwykłych procesorów. Jeśli natomiast liczbę błędów zwiększymy o 8%, to układ będzie 15-krotnie bardziej wydajny - mówi Avinash Lingamneni, współpracownik profesora Palema.

Tego typu procesory nie nadają się, oczywiście, do wielu zastosowań. Ale będzie ich można używać tam, gdzie nie jest wymagana duża precyzja obliczeń. Istnieją plany wbudowania ich w tanie tablety, które trafią do uczniów z najuboższych regionów Indii. Procesor probabilistyczny dobrze sprawdzi się też w roli układu przetwarzającego obraz wideo, szczególnie w urządzeniach o niewielkim wyświetlaczu na którym można tolerować niedoskonałości obrazu.

Komentarze (5)

sig, 21 maja 2012, 18:59

A jak uruchomić na czymś takim jakikolwiek system operacyjny? Moim zdaniem nada się co najwyżej na sprzętowy generator liczb losowych, tam błędy będą wręcz pożądane. No chyba że będą 2 procki, jeden dla OS-a a drugi np do wspomnianego dekodowania za pomocą specjalnej aplikacji potrafiącej z niego korzystać (coś jak dzisiaj CUDA, tyle że te nie robią błędów. Swoją drogą jak tam porównanie tego typu procesora do shaderów z nowoczesnych GPU?).

sator666, 22 maja 2012, 07:53

Bardzo przydałby mi się taki procesor jako drugi w systemie, np. do procesu uczenia sztucznej sieci neuronowej! Tu nie potrzeba suber dokładnych wyników a liczy się szybkość!

Jajcenty, 22 maja 2012, 10:49

To nie możesz użyć GPUs? Ten chip przydałby się do uczenia neurokrzemków w warunkach głodu elektronowego.

Jajcenty, 22 maja 2012, 10:55

Tak mi przyszło do głowy - jeśli wszystko liczyć dwa razy (lub równolegle na dwóch kościach) a wyniki akceptować jeśli są zgodne to i tak z tych 15 razy sporo nam zostaje. Jeśli natura błędów jest losowa to nie powinno być problemu w uzgodnieniu wyniku. Nie wiem jak to się da zastosować do zadań czasu rzeczywistego ale brzmi zachęcająco.

Skotos, 22 maja 2012, 11:38

Bez problemu. Rozumiem pomysł raczej tak, że przy instrukcjach zmiennoprzecinkowych z dużą dokładnością wyników, gdzie stosowane są skomplikowane i mocożerne konstrukcje lub kaskady poleceń w RISC pojawiają się błędy.

OSy w sumie nie potrzebują działań na liczbach rzeczywistych, więc będą działały :-)